Verilog 延迟模型

关键词: 分布延迟, 集总延迟, 路径延迟

之前大部分仿真都是验证数字电路功能的正确性,信号传输都是理想的,没有延迟。但是实际逻辑元器件和它们之间的传输路径都会存在延迟。因此,必须检查设计中的延迟是否满足实际电路的时序约束要求。可以用时序仿真的方法来检查时序(timing),即在仿真时向元件或路径中加入和实际相符的延迟信息,并进行相关计算来确定时序是否满足。

静态时序分析 (Static Timing Analysis, STA),也是一种时序验证的技术。它不关心逻辑功能的正确与否,只对设计中的时序进行计算分析,来确定电路中是否存在违反 (violation) 时序约束的设计。STA 分析速度快,能够快速定位问题,但会忽略一些异步的问题。

所以 "STA + 时序仿真"是一种相对完善且安全的时序验证方法。本教程只对时序仿真做一些简单的介绍,暂时对 STA 不做讨论。

延迟模型主要有 3 种:分布延迟、集总延迟(lumped) 和路径延迟。

分布延迟

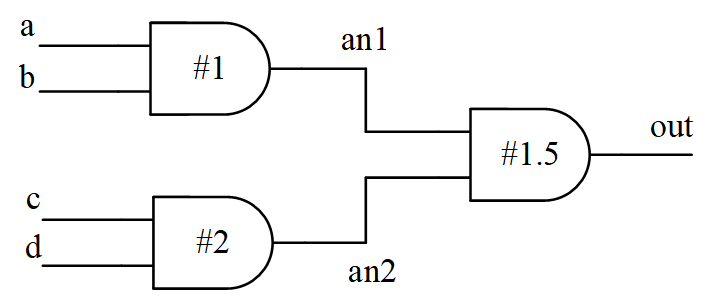

分布延迟需要给电路中每个独立的元件进行延迟定义,不同的路径有不同的延时,如下图所示。

分布延迟的 Verilog 模型和例化逻辑门单元并指定延迟值的方式基本一致。

module and4(

output out,

input a, b, c, d);

wire an1, an2 ;

and #1 (an1, a, b);

and #2 (an2, c, d);

and #1.5 (out, an1, an2);

endmodule也可以使用连续赋值语句 assign 说明分布延迟。

module and4(

output out,

input a, b, c, d);

wire an1, an2 ;

assign #1 an1 = a & b ;

assign #2 an2 = c & d ;

assign #1.5 out = an1 & an2 ;

endmodule集总延迟

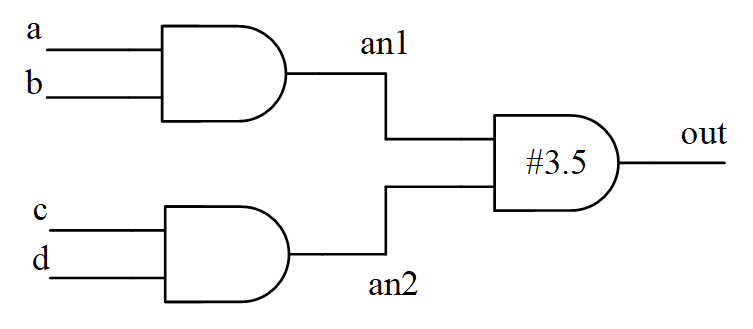

集总延迟是将全部路径累计的延时集中到最后一个门单元上。

到最后一个门单元上的延迟会因路径的不同而不同,此时取最大延时作为最后一个门单元的延时。

将上述分布延迟图转化为集总延迟图,如下所示。

集总延迟 Verilog 模型如下。

module and4(

output out,

input a, b, c, d);

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and #3.5 (out, an1, an2); //set the max delay at the last gate

endmodule路径延迟

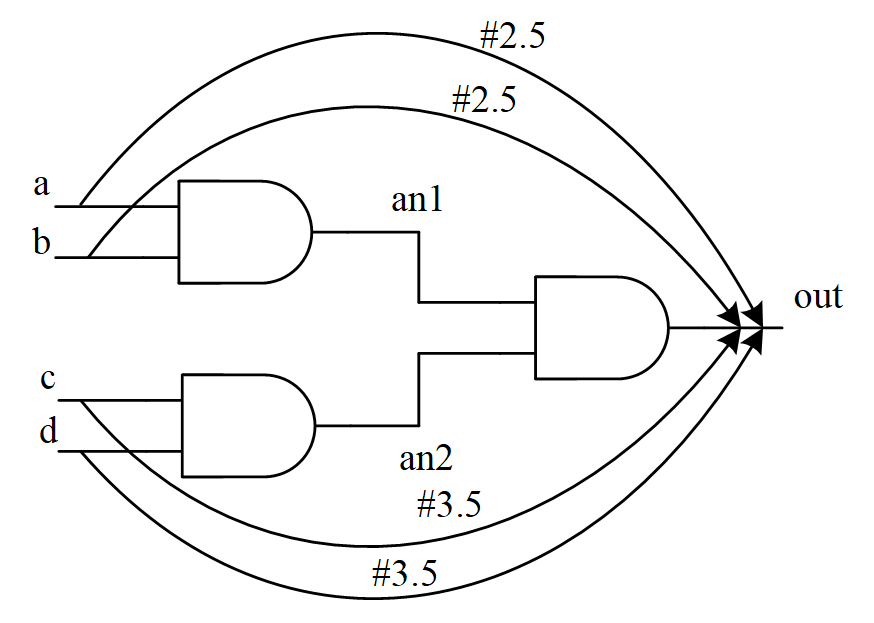

路径延迟是对每个输入引脚到每个输出引脚的所有路径指定延迟时间。

路径延迟示意图如下。

路径延迟模型需要用关键字 specify 来定义。

路径延迟 Verilog 模型如下,具体定义方法将在下一节详细介绍。

module and4(

output out,

input a, b, c, d);

specify

(a => out) = 2.5 ;

(b => out) = 2.5 ;

(c => out) = 3.5 ;

(d => out) = 3.5 ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule延迟模型比较

- 分布延迟:分布延迟将延迟时间分散在了每一个门单元上,但仍然不能描述基本单元中不同引脚上延时的差异。当设计规模变大时,结构将变的复杂。

- 集总延迟:该方式模型简单,适用于小规模的电路,但是不能描述输入端到输出端不同路径的延迟。

- 路径延迟:指定了引脚到引脚的延迟,延迟信息比较齐全。虽然信息比较多,但对于大规模电路也更容易实现。因为设计者无需关心模块内部的实现逻辑,只需要了解输入到输出引脚的延迟即可。即便模块内部逻辑有所改变,路径延迟的说明也可以保持不变。

所以,大多数逻辑门单元库中的延迟信息,都是以路径延迟的方式给出的。很多集成模块,也可以从其数据手册中直接获取到路径延迟,十分方便。

点击这里下载源码

免费AI编程助手

免费AI编程助手

更多建议: